本文是北京大学人工智能研究院类脑智能芯片研究中心唐希源研究员团队在国际集成电路设计领域顶级会议IEEE Custom Integrated Circuits Conference(CICC)上发表论文 A Calibration-Free 15-level/Cell eDRAM Computing-in-Memory Macro with 3T1C Current-Programmed Dynamic-Cascoded MLC achieving 233-to-304-TOPS/W 4b MAC的介绍。

北京大学博士后宋嘉豪为第一作者,唐希源研究员与王源教授为通讯作者。

不断发展的AI算法对边缘端硬件的算力与能效提出了挑战。传统计算架构执行AI算法的瓶颈在于数据搬运功耗,即“存储墙”问题。为了解决这一问题,将计算嵌入到存储单元中并在模拟域完成乘累加运算的模拟存算一体AI芯片被提出。模拟域存算一体芯片可以分为电流型设计、电荷型设计以及时间型设计。其中,电流型设计可以模拟计算因其高面积效率和高并行等特点,受到研究人员的青睐。

尽管近年不断有新型的电流型存算一体芯片被提出, 然而电流型存算一体芯片的根本问题并未得到解决。目前的电流型模拟存算一体芯片受到晶体管非理想性的限制,无法在小电流下实现精确计算,因而存在着计算精度、能效瓶颈与鲁棒性多重挑战,其应用场景严重受限。

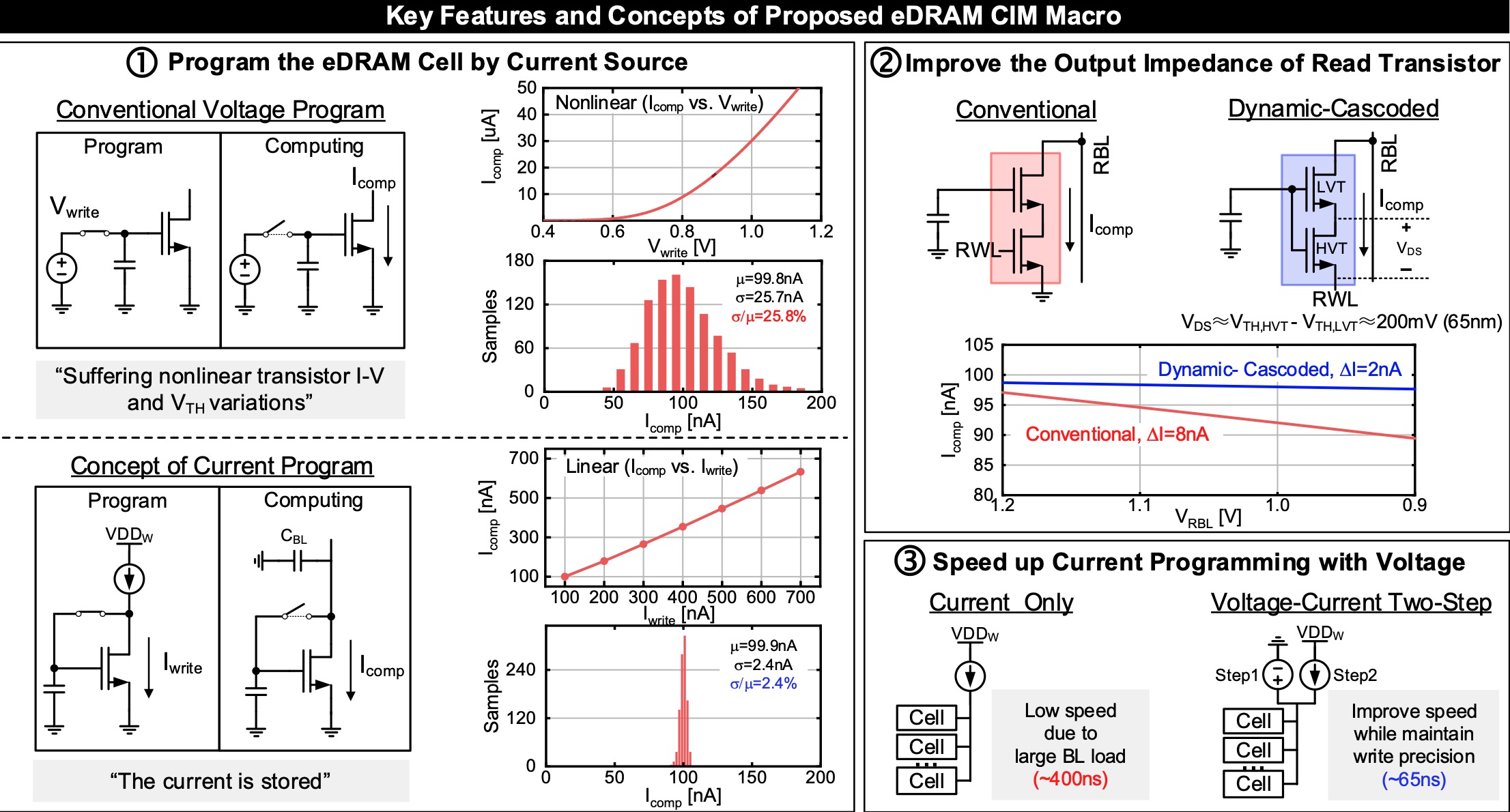

图1 所提出电流型存算一体设计的关键技术

针对这一系列挑战,唐希源课题组从电流型模拟存算一体电路的误差产生机制入手,首次提出了电流编程技术。如图1所示,该技术利用编程电流产生自校准的权重电压,实现多值模拟权重的高精度编程。同时,课题组提出了电压-电流两步编程模数,利用编程电压进行快速初步写入并用编程电流完成精确写入,大幅提高了多比特权重编程速度。此外,课题组提出了自偏置共源共栅读出结构,在无需额外偏置电路的情况下大幅增加了存储单元读出精度,降低了计算电流的对位线电压的敏感度。这三项技术使得电流型多值模拟存算单元可以无需校准地工作在小于1uA的计算电流下,突破了电流型存算一体电路的精度与能效瓶颈,并大幅提升其鲁棒性。

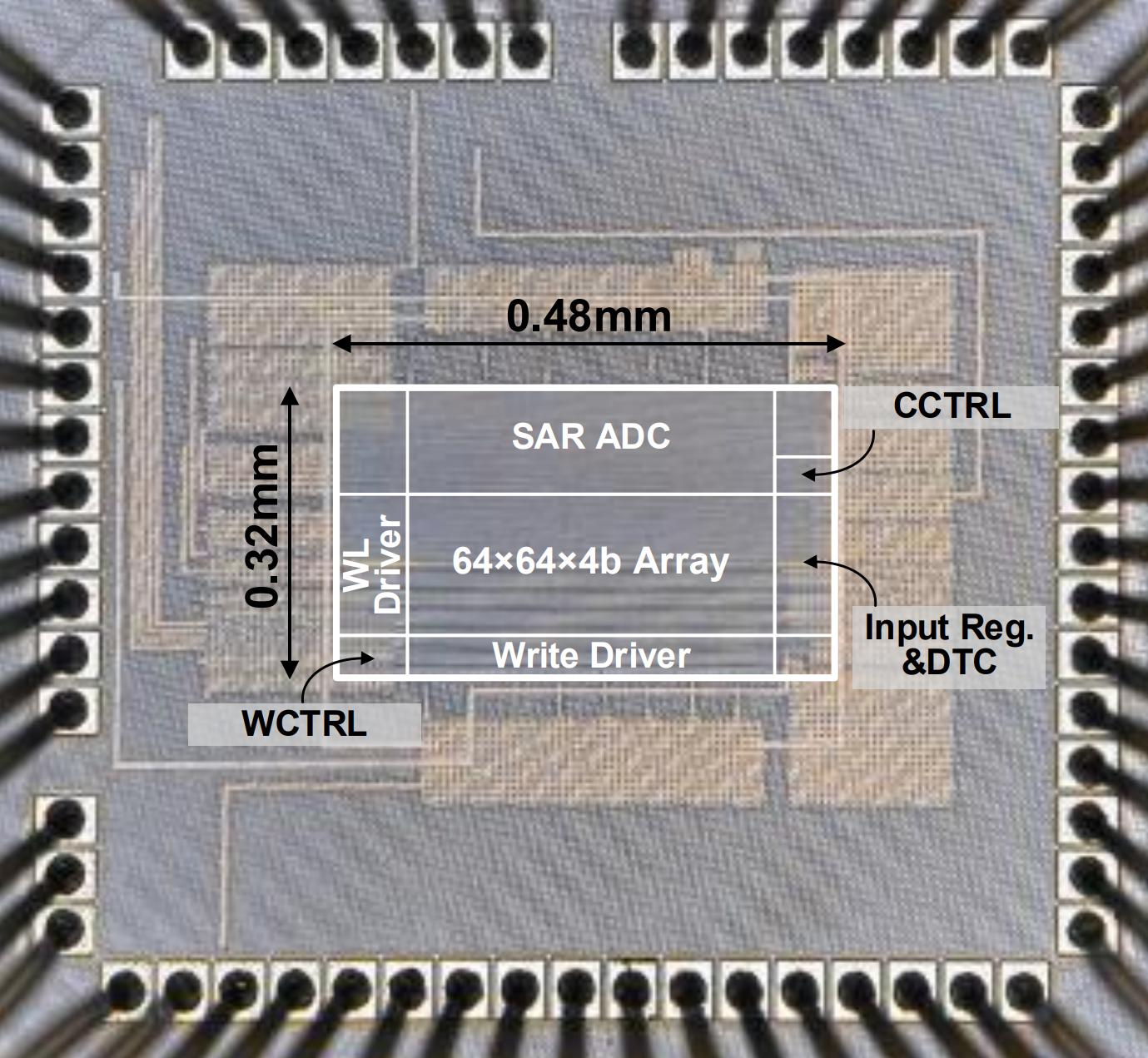

基于上述创新设计,课题组研制了一款基于65 nm CMOS工艺的电流型eDRAM模拟存内一体芯片(图2),并对芯片进行了性能测试与汇报。在4-b输入/4-b权重/5-b输出精度的情况下,16Kb容量的原型芯片实现了233-304 TOPS/W的计算能效与2.963 TOPS/mm2的单位面积算力,达到了电流型存算一体芯片中的国际领先水平。该创新通过将模拟权重的编程与计算统一到了电流域,大幅提高了模拟存算一体电流的计算精度与鲁棒性,可应用于边缘端AI计算场景。

图2 电流编程存算一体芯片显微照片

会议介绍

在集成电路芯片设计领域,IEEE固态电路协会(Solid-State Circuits Society)主办的定制集成电路会议(CICC)是IC设计领域顶级会议之一,以论文录用率低、作品创新性和实用性强著称,每年吸引全球范围内大量学术界、工业界研发人员的关注和参与。会议内容涉及模拟电路设计、生物医学、传感器、显示器和MEMS,数字和混合信号SoC/ASIC/SIP, 嵌入式存储器件等方面,重点讨论如何解决集成电路设计问题的方法,以提高芯片各项性能指标。

团队介绍

唐希源助理教授于2021年加入北京大学人工智能研究院/集成电路学院从事模拟、混合信号芯片、人工智能芯片研究。2019年于德州大学奥斯汀分校取得博士学位,2019-2021年在德州大学奥斯汀分校从事博士后研究。

课题组主页:https://tangresearch.top/

课题组常年招收志在探索未知的研究生与博士后,请直接邮件联系。

Email:xitang at pku.edu.cn